產品&解決方案

科楠科技以創新驅動研發,致力于為客戶提供最有競爭力的產品和解決方案,持續為客戶帶來最大價值。

通用LVDS數據模擬源

時鐘與數據相位關系可調,步進1ns

自定義LVDS位寬

LVDS級聯功能

設備體積小,攜帶方便

產品簡介

產品簡介

設備尺寸為:240mm*244mm*49mm(長*寬*高),電源集成在整機中。正面為開關及控制接口,背面為六路用戶LVDS接口。主要由FPGA、ARM、以太網PHY、USB PHY、USB Hub、Flash、時鐘芯片、DDR芯片、mSATA硬盤等組成。

設備可實現24路LVDS數據發送,發送數據存放在內置固態硬盤中。可通過多臺設備級聯實現接口數量擴展。上位機內置數據生成功能,可根據客戶要求生成各種幀格式的數據文件。

l 接口類型:LVDS,接口位寬:20-bit(可拆分),時鐘速率:100KHz-100MHz可調;時鐘相位可調整

l 接口數量:6個數據發送接口,1個自檢接收接口

l 每個接口對應一個mSATA固態硬盤存儲數據

l 通過USB3.0接口或千兆網口對設備進行控制,設備可級聯

l 通過構造數據文件實現正逆程變化的數據發送

產品框架

產品框架

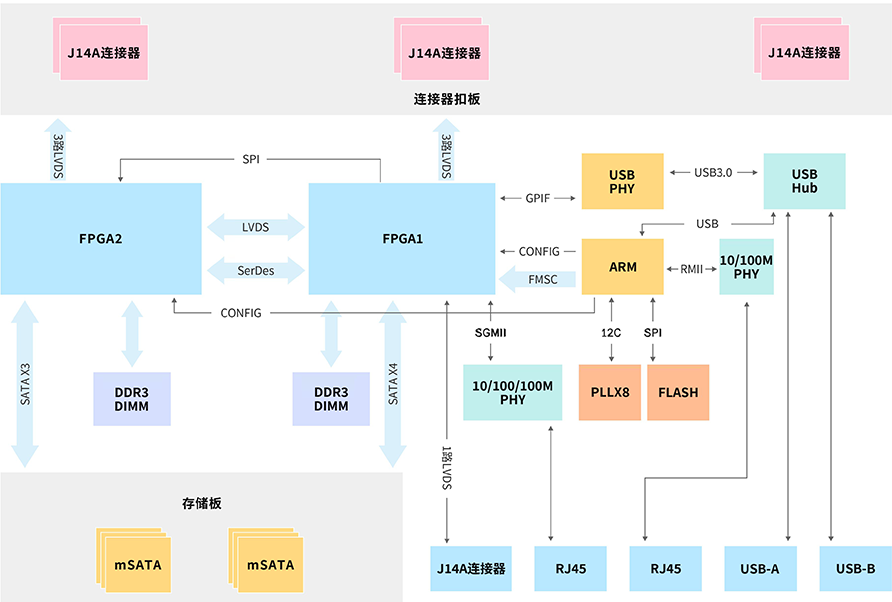

設備由1塊主板和2塊扣板組成,主板上主要由FPGA、以太網PHY、USB PHY、USB Hub、ARM、Flash、PLL`等組成。每塊設備對外出6路LVDS輸出、1路LVDS輸入,為減小設備面積,對外LVDS連接器采用上下兩層設計,主板上出3路輸出和1路輸入,連接器扣板上出3路輸出。主板對外出一個千兆網口和2個USB口,2個USB口通過Hub引出,用來實現多個設備級聯功能,用戶通過千兆以太網或者USB口將發送的數據導入設備,導入的數據存在存儲板上的mSATA盤中,每個盤對應1路LVDS,6路LVDS需要6個mSATA盤,為了減少主板面積,3個mSATA盤放在主板上,另外3個放在扣板上。FPGA外掛了大容量DDR3內存條,用于緩存數據。主板上的ARM用于時鐘配置、版本升級、命令解析、狀態上報等,ARM對外出百兆網口或者USB接口與計算機相連,接收命令、FPGA版本文件、上報狀態均通過該接口。系統框圖如下圖所示:

產品參數

產品參數

l 接口類型:LVDS,接口位寬:20-bit(可拆分),時鐘速率:100KHz-100MHz可調;時鐘相位可調整

l 接口數量:6個數據發送接口,1個自檢接收接口

l 每個接口對應一個mSATA固態硬盤存儲數據

l 通過USB3.0接口或千兆網口對設備進行控制,設備可級聯

l 通過構造數據文件實現正逆程變化的數據發送

相關產品推薦

產品&解決方案 >

產品&解決方案 >

深圳市南山區西麗街道打石一路深圳國際創新谷7棟B座8樓

深圳市南山區西麗街道打石一路深圳國際創新谷7棟B座8樓 +86-755-82513818

+86-755-82513818 +86-755-82513868

+86-755-82513868